VME DAQ Rawdata Format

Raw data is stored as is from the hardware. Minimal quantum of data is 4 bytes (32 bits). Intel byte order is used.

Contents

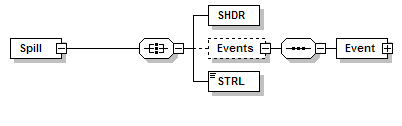

Data Stream Structure

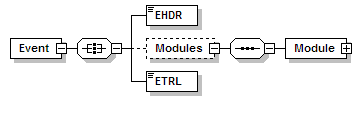

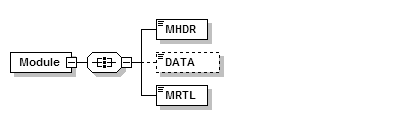

Raw data stream is split in spills beginning with SHDR and ending with STRL, the data in between is a sequence of zero or more events. Event begins with EHDR and ends with ETRL. The data between event header and trailer is a sequence of module data blocks. Module data starts with MHDR and ends with MTRL. Module data is any number of words of type DATA.

Data Types

Raw data word structure by bits, MSB left |

|||||||||||||||||||||||||||||||

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

type |

data |

||||||||||||||||||||||||||||||

Type is one of the following:

type, bin |

type, hex |

code |

description |

0000 |

0 |

DATA |

Module data |

0001 |

1 |

||

0010 |

2 |

||

0011 |

3 |

||

0100 |

4 |

||

0101 |

5 |

||

0110 |

6 |

||

0111 |

7 |

||

1000 |

8 |

MHDR |

Module header |

1001 |

9 |

MTRL |

Module trailer |

1010 |

A |

EHDR |

Event header |

1011 |

B |

ETRL |

Event trailer |

1100 |

C |

SHDR |

Spill header |

1101 |

D |

STRL |

Spill trailer |

1110 |

E |

STAT |

Status |

1111 |

F |

PADD |

Padding |

Data Word Details

SHDR |

|||||||||||||||||||||||||||||||

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

1 |

1 |

0 |

0 |

spill type |

reserved |

reserved |

|||||||||||||||||||||||||

STRL |

|||||||||||||||||||||||||||||||

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

1 |

1 |

0 |

1 |

spill type |

reserved |

reserved |

|||||||||||||||||||||||||

Spill type:

- 0 - Normal data

- 1 - End of spill data

EHDR |

|||||||||||||||||||||||||||||||

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

1 |

0 |

1 |

0 |

reserved |

event number |

||||||||||||||||||||||||||

ETRL |

|||||||||||||||||||||||||||||||

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

1 |

0 |

1 |

1 |

readout_status |

word count |

||||||||||||||||||||||||||

readout_status bits:

- [0] - timeout

- [3:1] - reserved

MHDR |

|||||||||||||||||||||||||||||||

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

1 |

0 |

0 |

0 |

event number |

|||||||||||||||||||||||||||

MTRL |

|||||||||||||||||||||||||||||||

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

1 |

0 |

0 |

1 |

checksum |

AE# |

TE# |

RE# |

RO# |

word count |

||||||||||||||||||||||

- AE# - module access error (active low)

- TE# - module ttc error (active low)

- RE# - module readout error (active low)

- RO# - module readout overflow (active low)

- checksum is CRC-8 (ETSI EN 302 307, 5.1.4) of module data including MHDR but not including MTRL (available in firmware rev. 14019 and later)

STAT |

|||||||||||||||||||||||||||||||

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

1 |

1 |

1 |

0 |

type |

status data |

||||||||||||||||||||||||||

status types:

- 0000 - reserved

- 0001 - Thermometry, data bits 23:20 - id, bits 19:0 is module temperature in 1/256 deg C steps

PADD |

|||||||||||||||||||||||||||||||

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

1 |

1 |

1 |

1 |

0xFFFFFFF |

|||||||||||||||||||||||||||