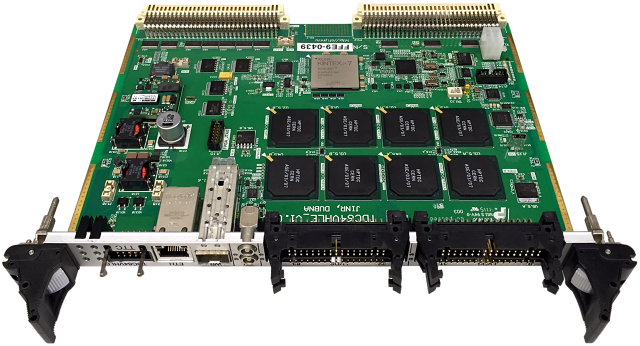

TDC64VHLE

TDC64VHLE is 64-channel 25 ps multihit timestamping TDC

Specification

- 64 channels, differential 100 Ω input (LVDS only)

TDC: timestamping, 25ps bin size*

- +5 V 0.85 A (measured on pcb V2)

- +3.3 V 9 A (measured on pcb V2)

Interface

- VXS (time, trigger and data using Fe-Link)

- VME64x interface

- VMEDAQ TTC bus (Clock, Trigger)

Stadalone option

- SFP serial interconnect (Ethernet)

Time Synchronization by White Rabbit or FE-Link

Programmers docs - TODO

TODO:

- Registers description (Eth/VME)

- Data format description (Eth/VME)