VMEDAQ User Manual

Contents

Overview

Installation

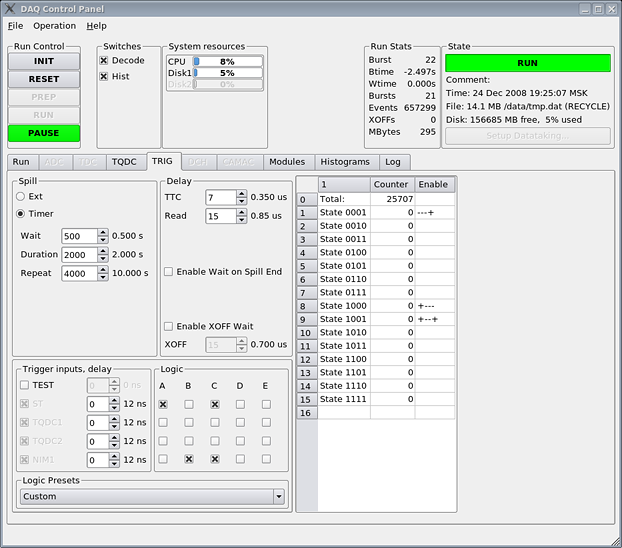

Run Control

INIT - Initialize hardware. SYSRESET on VME bus. Auto-detect modules.

RESET - Clear counters and FIFOs. Clear histograms. Stop data taking if in progress.

PREP - Prepare to run: load run-mode settings

RUN - Start or resume data taking

PAUSE - Temporarily disable data taking

Information Panels

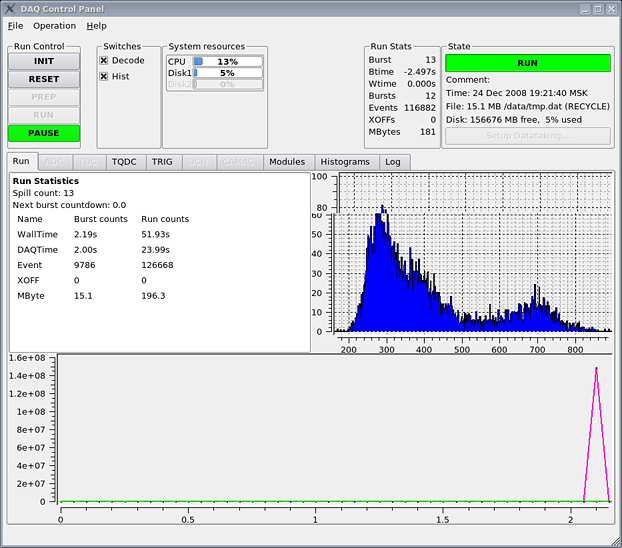

Run

Event size histogram: shown the distribution of event size in words for the last spill.

Spill graph shows the instant raw data throughput.

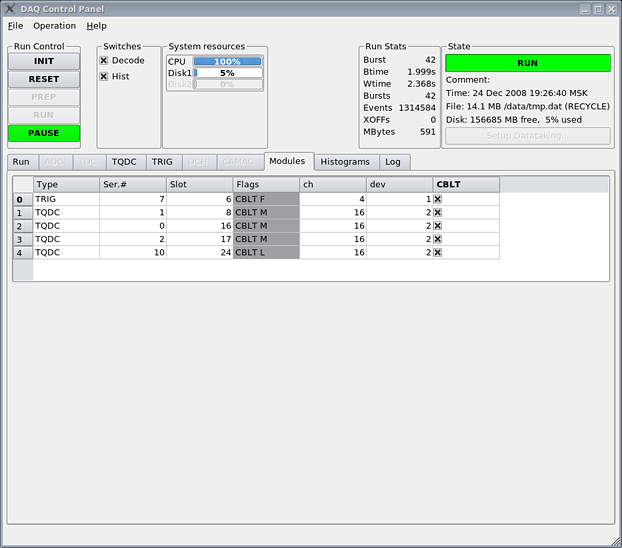

Modules

List of modules found while Auto-detection. Slot number is either VME64x geographical address or programmed value. Serial number is used for individual module calibration data. Flags column highlights red if any error is detected or module is not configured. Error is usually indicated for HPTDC based modules until they have configuration loaded in PREP state, it is normal.

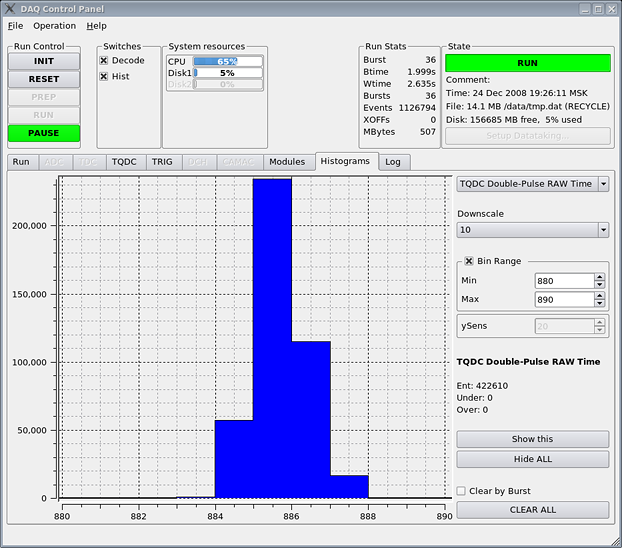

Histograms

Detailed description of VMEDAQ Histograms.

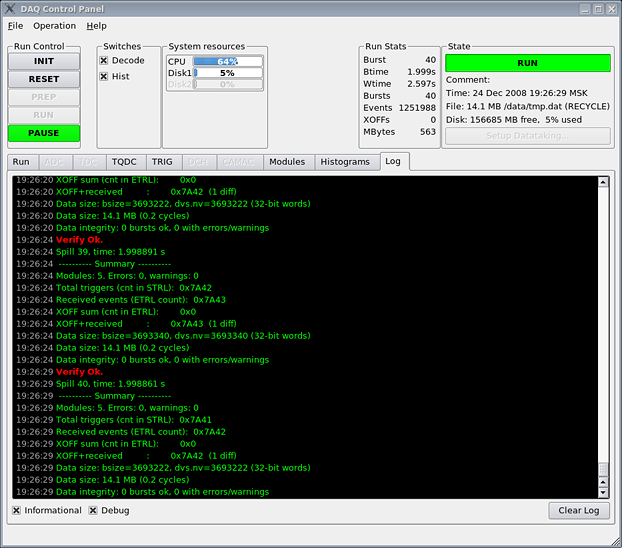

Log

Module Configuration

TRIG

Hardware modules: TTCM

ADC

TDC

Hardware modules: TDC-96, PhTDC, MTDC-64

Understanding Trigger Matching

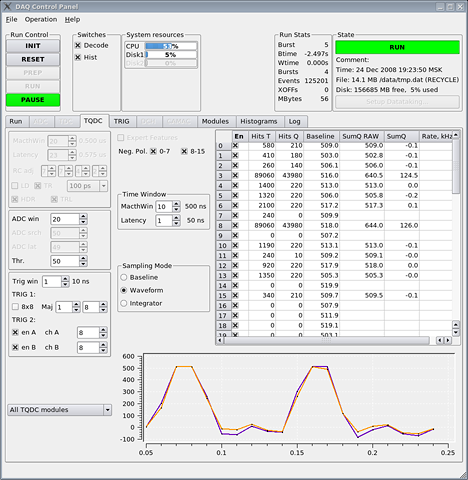

TQDC

Hardware modules: TQDC-16 GUI Controls

Waverofm settings

- ADC win - number of ADC samples for one pulse

- Thr. - input discriminator threshold in mV (highpass filtered)

Local Trigger Settings

- Trig win - trigger pulse shaping time (coincidence time)

- 8x8 - when enabled, logic AND, otherwise logic OR

- Maj - majority

- en A, en B, ch A, ch B - when enabled, route input signal of channel A/B to ST trigger line and exclude from TQDCn trigger line

Input Signal Polarity Switch

- 0-7 - set for negative polarity for channels 0-7

- 8-15 - same for channels 8-15

Time Window

- Matchwin - width of trigger matching window

- Latency - time offset of matching window end

Sampling Mode

- Baseline - calibration. Use with TEST trigger.

Waveform - oscilloscope mode, ADC win samples are read for each input pulse

Integrator - no waveform data, only arithmetic sum of ADC win samples

Combo box for threshold set selection:

- All TQDC modules - set threshold for all modules.

- TQDC n - set threshold for selecterd module only.

All other settings are set for all TQDC modules.

Channel Table

- Enable each single channel - both trigger and data readout.

DCH

Hardware modules: BRICBOX, BRIC

CAMAC

Obsolete. Not supported.

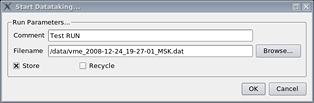

Data Storage Setup

Raw data is stored as-is in VME Raw Data Format.

Press Storage Setup, select destination file name and check desired options:

- Store - enable storage, i.e. write data to disk

- Recycle - enable external storage software

In normal mode, when Recycle is not checked, raw data file is appended while spill is in progress. File is growing. Run Reset does not clear the file. Check periodically for free disk space.

In Recycle mode, raw data is stored to temporary file and every new spill temporary file is renamed to specified data file. External storage program may watch the modification of data file. Data file in Recycle mode does not grow every next spill.

DNL Compensation (TQDC only)

Since version 1.0-7.10459 the HPTDC DNL compensation is available for TQDC modules. Place calibration file http://afi-svn.jinr.ru/svn/soft/vmedaq/trunk/other/tqdc_inl.txt in the directory you run vmegui from. Start vmegui, press Clear Counts. Calibration is loaded. You may check the time resolution improvement by providing two signals with known phase difference and check the TQDC Double-Pulse Time, ns histogram. The distribution should have less than 50 ps FWHM (width at half maximum). If not, check threshold and signal level, make sure you run vmegui in the same directory where you put the calibration file tqdc_inl.txt.