U40VE_RC RAW Data Format

Data Types

Data types |

|

2 |

TAI timestamp |

3 |

Trigword |

Normal spill data

TAI Timecode

Timecode in TAI (International Atomic Time) scale is received by White Rabbit interface.

2 - TAI Timestamp |

|||||||||||||||||||||||||||||||

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

2 |

TAI ns [27:0] |

||||||||||||||||||||||||||||||

2 |

TAI seconds [23:0] |

TAI flags |

TAI ns [29:28] |

||||||||||||||||||||||||||||

2 |

0 |

TAI seconds [39:24] |

|||||||||||||||||||||||||||||

TAI flags: 2 - timecode is valid, otherwise invalid.

3 - Trigword |

|||||||||||||||||||||||||||||||

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

3 |

0 |

trig source[7:0] |

LVDS_IN [15:0] |

||||||||||||||||||||||||||||

trig source[7] - internal periodical

trig source[6] - internal random

trig source[5-1] - 0

trig source[0] - external

4 - AUX Counters |

|||||||||||||||||||||||||||||||

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

4 |

Trig candidates [27:0] |

||||||||||||||||||||||||||||||

4 |

Trig accepted [27:0] |

||||||||||||||||||||||||||||||

4 |

Before rejected [27:0] |

||||||||||||||||||||||||||||||

4 |

After rejected [27:0] |

||||||||||||||||||||||||||||||

4 |

Trig reject counter [27:0] |

||||||||||||||||||||||||||||||

4 |

Beam trig all counter [27:0] |

||||||||||||||||||||||||||||||

4 |

Beam trig available counter [27:0] |

||||||||||||||||||||||||||||||

All AUX counters are reset by spill leading edge signal

Trig candidates - trigger candidates(without before/after protection)

Trig accepted - DAQ triggers which passed before/after protection

Before rejected - numver of triggers rejected by before protection

After rejected - numver of triggers rejected by after protection

Trig reject counter - unused

Beam trig all counter - all available triggers from T0 unit

Beam trig available counter - same as prev. AND DAQ NOT BUSY

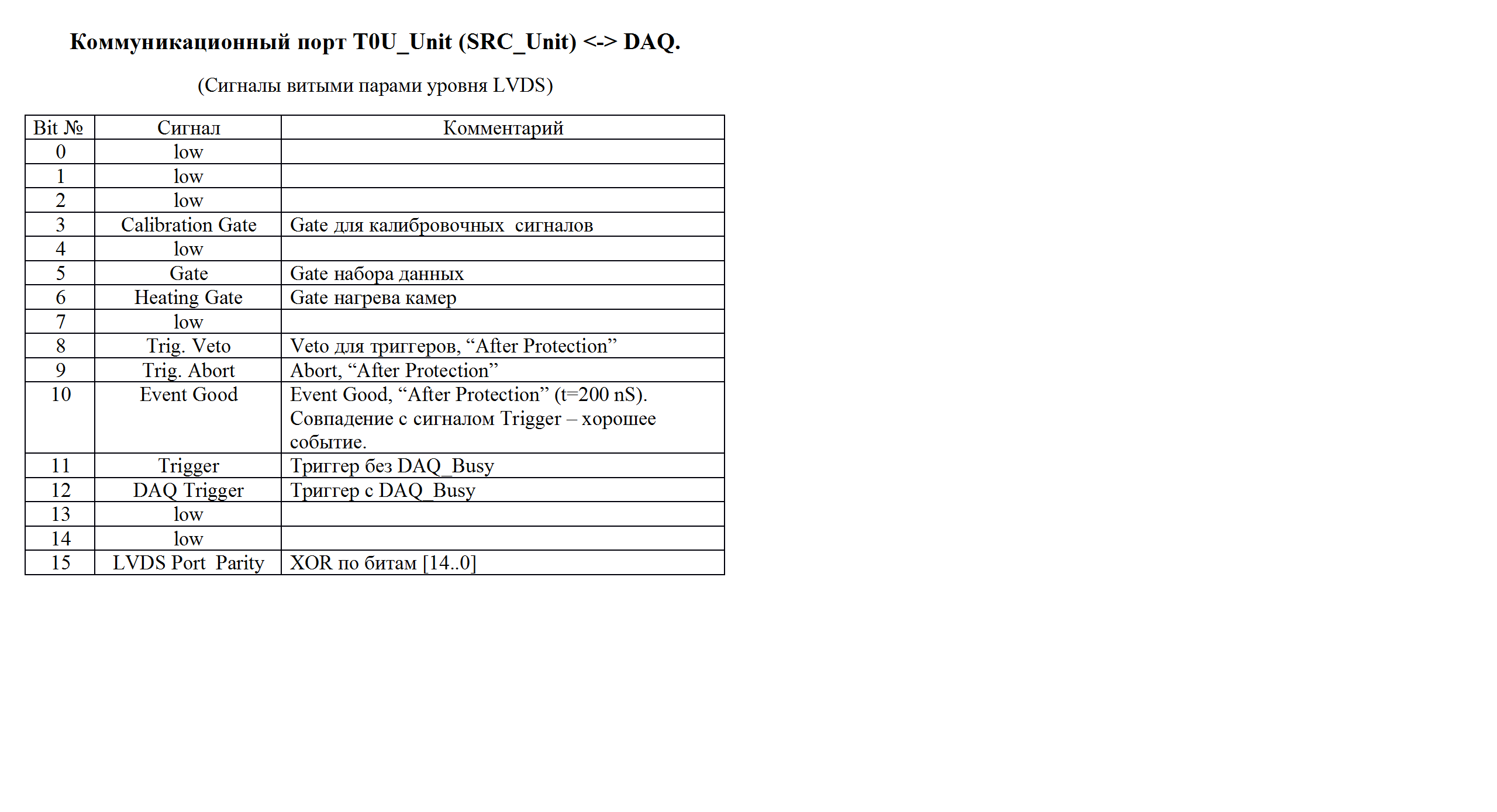

LVDS bus

LVDS bus (for session 55 after SRC)

LVDS bus |

||

Bit |

Polarity |

Name |

0 |

+ |

Low |

1 |

+ |

Low |

2 |

+ |

Low |

3 |

+ |

outOs_Pul1 |

4 |

+ |

Low |

5 |

+ |

outOs_Gate |

6 |

- |

outOs_Pul2 |

7 |

- |

Low |

8 |

- |

Prot |

9 |

- |

Trigger_Abort |

10 |

- |

Evnt_Good |

11 |

- |

Trigger |

12 |

- |

BT |

13 |

- |

BC1 |

14 |

+ |

BC1_or_VC |

15 |

+ |

LVDS_Port_Parity[14..0] |